# **RENSIT:**

## RadioElectronics. NanoSystems. Information Technologies

Journal "Radioelectronics. Nanosystems. Information Technologies" (abbr. RENSIT) publishes original articles, reviews and brief reports, not previously published, on topical problems in radioelectronics (including biomedical) and fundamentals of information, nano- and biotechnologies and adjacent areas of physics and mathematics.

Designed for researchers, graduate students, physics students of senior courses and teachers. It turns out 4 times a year (that includes 4 issues)

Authors of journal are academicians, corresponding members and foreign members of Russian Academy of Natural Sciences (RANS) and their colleagues,

as well as other russian and foreign authors on presentation of their manuscripts by the members of RANS, which can be obtained by authors before sending articles to editors.

And also after its receiving - on recommendation of a member of editorial board of journal, or another member of Academy of Natural Sciences, that gave her opinion on article at request of editor. The editors will accept articles in both **Russian and English** languages.

Articles are internally peer reviewed (**double-blind peer review**) by members of the Editorial Board. Some articles undergo external review, if necessary.

Journal RENSIT is included in the **DB SCOPUS, EBSCO Publishing,** in the international abstracts database -**Ulrich's International Periodicals Directory**,(USA, New York, http://www.ulrichsweb.com), in the **AJ and DB VINITI RAS** (http://www.viniti.ru), and DB **Russian Science Citation Index (RSCI** http://elibrary.ru/project\_ risc.asp). Included in the **List of Higher Attestation Comission** (No. 2204 dated July 17, 2023: K1 in 18 groups of specialties) of Science and Higher Education Ministry of the Russian Federation.

**Full-text content** is posted in the DB of the **Russian Scientific Electronic Library** - information resource on the Internet http://elibrary.ru and is available for registered users. And also - in Open Access **CyberLeninka NEB** of Russian Federation http://cyberleninka.ru.

On journal's website http://www.rensit.ru posted metadata publications and **RENSIT: Radioelectronics. Nanosystems. Infomation Technologies - english version** (cover-to-cover translation) of journal, which is a party to **CrossRef.**

> The founder - the **Russian Academy of Natural Sciences** Publisher - Publishing Center of the Russian Academy of Natural Sciences Publisher Address: 29/16, Sivtsev Vrazhek lane, Moscow 119002, Russian Federation

#### CONTENTS

# RADIOELECTRONICS

#### DEVELOPMENT AND APPLICATIONS OF A MICROCONTROLLER-BASED LOGIC TESTER FOR INTEGRATED CIRCUITS IN THE 74XX SERIES

# NANOPHOTONIC DEVICES FOR RADIO OVER FIBER

TECHNOLOGIES IN TELECOMMUNICATIONS NETWORKS Hanan Mahmood Shukur Ali, Sirwan Kareem Jalal, Maher Waleed Saab, Sharmeen Izzat Hassan, Ghazwan Saleem Naamo Ghno, Saif Saad Ahmed,

#### Salama Idris Mustafa, Abdymanap Z. Pirmatov ...... 589 NANOSYSTEMS

#### **INFORMATION TECHNOLOGIES**

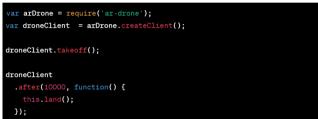

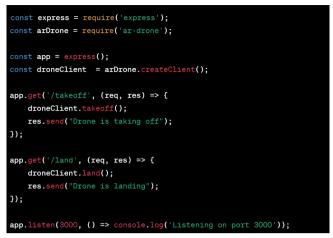

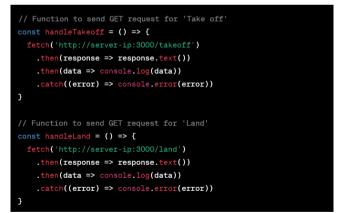

ADVANCING DRONE CONTROL INTERFACES: IMPLEMENTING JAVASCRIPT FOR MOBILE CONNECTIVITY WITH THE PARROT AR DRONE 2.0.

Mohammed Khaleel Hussein, Ali Ihsan Alanssari, Haider Khalil Easa, Ali Majid, Ahmed Isam Al-Hatem, Nashwan Adnan Othman, Anmar Hameed Bloh, Mohammed Abdul Jaleel Maktoof, Kudaiberdi G. Kozhobekov .... 617

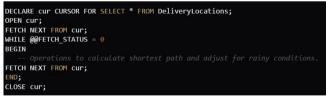

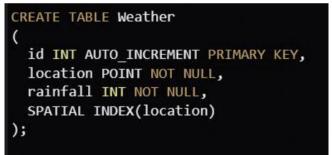

ENHANCING DRONE STABILITY IN ADVERSE WEATHER CONDITIONS: A NOVEL MYSQL-BASED APPROACH FOR BALANCING UAVS IN RAIN

AN EXHAUSTIVE EXAMINATION OF ARCHITECTURAL METHODS FOR HARDWARE SECURITY MECHANISMS IN IOT DEVICES

SCALABLE NETWORK-ON-CHIP (NOC) DESIGNS FOR HIGH-PERFORMANCE COMPUTING SYSTEMS THEIR TRENDS AND CHALLENGES

NEXT-GENERATION FPGA ARCHITECTURES THROUGH BALANCING PERFORMANCE, FLEXIBILITY, AND POWER CONSUMPTION

QUANTUM COMPUTING IMPACT ON TRADITIONAL

#### COMPUTER ARCHITECTURE MODELS

| Salih Mahmoud Attya, Suhad Qasim G. Haddad, Hamid Kareem Radam Al- |

|--------------------------------------------------------------------|

| Zaidi, Wafaa Mustafa Hameed, Nabaa Latif 691                       |

#### RUSSIAN ACADEMY OF NATURAL SCIENCES

DEPARTMENT OF RADIOELECTRONICS, NANOPHYSICS AND INFORMATION TECHNOLOGIES

# **RENSIT**:

RADIOELECTRONICS. NANOSYSTEMS. INFORMATION TECHNOLOGIES.

2024, vol. 16, № 5

FOUNDED IN 2009 4 ISSUES PER YEAR MOSCOW

PROBLEMS

Editor-in-Chief VLADIMIR I. GRACHEV grachev@cplire.ru Deputy Chief Editor Alexander S. Ilyushin, DrSci, MSU Deputy Chief Editor Sergey P. Gubin, DrSci, IGIC RAS Executive Secretary Vadim V. Kashin, PhD, IRE RAS vvkashin@cplire.ru

EDITORIAL BOARD

Anatoly V. Andreev, DrSci, MSU Vladimir A. Bushuev, DrSci, MSU Vladimir A. Cherepenin, DrSci, IRE Alexander S. Dmitriev, DrSci, IRE Yuri K. Fetisov, DrSci, MIREA Yuri V. Gulvaev, DrSci, acad.RAS, IRE Yaroslav A. Ilyushin, DrSci, MSU Anatoly V. Kozar, DrSci, MSU Vladimir V. Kolesov, PhD, IRE Albina A. Kornilova, PhD, MSU Vladimir A. Makarov, DrSci, MSU Alexander V. Okotrub, DrSci,SB RAS Aleksey P. Oreshko, DrSci, MSU Igor B. Petrov, DrSci, CM RAS, MIPT Alexander A. Potapov, DrSci, IRE Vyacheslav S. Rusakov, DrSci, MSU Alexander S. Sigov, DrSci,ac.RAS, MIREA Eugeny S. Soldatov, PhD, MSU Arkady B. Tsepelev, DrSci, IMET Lkhamsuren Enkhtor, DrSci (Mongolia) Yoshiyuki Kawazoe, DrSci (Japan) Kayrat K. Kadyrzhanov, DrSci (Kazakhstan) Peter Paul Mac Kenn, DrSci (USA) Deleg Sangaa, DrSci (Mongolia) Andre Skirtach, DrSci (Belgium) Enrico Verona, DrSci (Italy)

#### ISSN 2414-1267

The journal on-line is registered by the Ministry of Telecom and Mass Cjmmunications of the Russian Federation. Certificate El. no. FS77-60275 on 19.12.2014

All rights reserved. No part of this publication may be reproduced in any form or by any means without permission in writing from the publisher.

©RANS 2024 EDITORIAL BOARD ADDRESS 218-219 of., 7 b., 11, Mokhovaya str., 125009 MOSCOW, RUSSIAN FEDERATION, TEL. +7 495 629 3368 Fax +7 495 629 3678 For Grachev

# DOI: 10.17725/j.rensit.2024.16.573

# Development and Applications of a Microcontroller-Based Logic Tester for Integrated Circuits in the 74xx Series

# Ali Ali Saber Mohammed

Al-Kitab University, https://www.uoalkitab.edu.iq/eng/ Kirkuk 36015, Iraq *E-mail: ali.a.saber@uoalkitab.edu.iq*

# Pshtiwan Shakor

Al-Qalam University College, https://alqalam.edu.iq/en/ Kirkuk 36001, Iraq *E-mail: pshtiwan.shakor@alqalam.edu.iq*

# Salam Khalaf Abdullah

Al-Nukhba University College, https://alnukhba.edu.iq/ Baghdad 10013, Iraq *E-mail: s.abdullah@alnukhba.edu.iq*

# Marwan Aziz Mohammed

Knowledge University, College of Engineering, https://knu.edu.iq/college?collegeId=5/ Erbil 44001, Iraq *E-mail: marwan.aziz@knu.edu.iq*

# Saad Jabbar Abbas

Al-Rafidain University College, https://en.ruc.edu.iq/ Baghdad 10064, Iraq *E-mail: saad.jabbar@ruc.edu.iq*

# Hayder Mahmood Salman

Al-Turath University College, https://alturathuniversity.com/ Baghdad 10013, Iraq *E-mail: haider.mahmood@turath.edu.iq*

# Mohammed Abdulkreem Mohammed

Alnoor University College, https://alnoor.edu.iq/en/ Nineveh 41012, Iraq *E-mail: mohammed.abdulkreem@alnoor.edu.iq*

# Romanbek K. Kalmatov

Osh State University, https://oshsu.kg/ Osh 723500, Kyrgyzstan *E-mail: rkalmatov@oshsu.kg*

Received January 27, 2024, peer-reviewed February 02, 2024, accepted February 09, 2024, published September 06, 2024.

Abstract – <u>Background</u>: In the electronics lab, testing equipment, especially those concentrating on integrated circuits (ICs), is critical. The ubiquitous usage of one or more integrated circuits (ICs) in electronic systems needs thorough testing of their functioning. <u>Objective</u>: This research aims to develop a Microcontroller-based Logic Tester specially tailored for most Integrated Circuits in the 74xx Series Logic Gates and uses the ATmega328. The primary purpose is to reproduce the attributes of a logic gate IC using the truth table, enabling the state of the IC's gates to be determined. <u>Methods</u>: Several design techniques were investigated. Following careful consideration, a single approach for implementation was selected. Modules were developed independently. After extensive testing and successful simulations, these components were combined to complete the project. <u>Results</u>: The designed IC tester is cost-effective and user-friendly; it examines ICs quickly

# 574 ALI A. SABER M., PSHTIWAN SHAKOR., SALAM K. ABDULLAH, MARWAN AZIZ M., SAAD JABBAR A., HAYDER MAHMOOD S., MOHAMMED ABDULKREEM M., ROMANBEK K. KALMATOV

# RADIOELECTRONICS

and presents findings to assess their functioning. The tester compares the output of each gate to a truth table. The results for both working and faulty ICs are shown on an LCD. <u>Conclusion</u>: In today's fast-changing electronics scene, an efficient digital IC tester that is both economical and dependable is critical. The project's conclusion provides a digital IC tester that simplifies the IC verification process for students and functions as a reliable tool in industrial settings.

Keywords: IC, IC digital, test IC, digital test, Arduino Nano, socket IC

#### UDC 53.087.92, 621.3. 049.77

*For citation:* Ali Ali Saber Mohammed, Pshtiwan Shakor, Salam Khalaf Abdullah, Marwan Aziz Mohammed, Saad Jabbar Abbas, Hayder Mahmood Salman, Mohammed Abdulkreem Mohammed, Romanbek K. Kalmatov. Development and Applications of a Microcontroller-Based Logic Tester for Integrated Circuits in the 74xx Series. *RENSIT: Radioelectronics. Nanosystems. Information Technologies*, 2024, 16(5):573-588e. DOI: 10.17725/j.rensit.2024.16.569.

**CONTENTS**

- 1. INTRODUCTION (574)

- 2. LITERATURE REVIEW (576)

- 3. Methodology (577)

- 4. Components and phases of designing a digital tester for integrated circuits (577)

- 5. TESTING WORKFLOW DESCRIPTION (583)

- 6. PRIMARY CHARACTERISTIC (583)

- 7. The tester novelty (584)

- 8. SIMILAR STUDIES ANALYSIS (584)

- 9. RESULTS (585)

- 10. DISCUSSION (585)

- 11. CONCLUSION (586)

- **R**EFERENCES (586)

# 1. INTRODUCTION

The need for a digital integrated circuit tester became apparent during an article on electrical principles and digital electronics. It was often unclear if faulty wiring, flawed design, or a malfunctioning integrated circuit was to blame for an issue. This effort aimed to simplify the process of verifying ICs for students [1,2].

The gates' dependability is determined only by the IC tester. The primary objective is to design a digital IC tester that is both more cost-effective and user-friendly than existing options. The ICs should be checked as soon as possible, and the results should be shown as soon as possible to demonstrate whether they are excellent or faulty [3]. Each gate's output is monitored and checked against the truth table as the microcontroller sends the appropriate input signal conditions to the gate's inputs. Based on that comparison, the IC is analysed to see if it is effective or defective. Testers of digital integrated circuits are primarily responsible for determining the correctness of the ICs' logic using a truth table and function table. The database is updated with the truth tables as the microcontroller is programmed. An LCD displays the test results, including the excellent and defective ICs. The test uses integrated circuits (ICs) from a set of fundamental logic gates. Users may choose from various IC testers available today [4,5].

In the electronics industry, testing tools are essential. When tinkering with electronic systems, it is common practice to use many ICs. In order to check whether an integrated circuit is functional, a digital IC tester based on a microcontroller is utilised. Testing a new product may be time-consuming and expensive in business [6]. The whole system has to be tested before it is placed into operation to eliminate the possibility of bugs and other unfavourable results. When several little faults are at the IC level, the system malfunctions and gives the wrong results. Thus, this work aims to develop a lightweight (less than Rs. 1000) but reliable digital IC tester [7].

The most important precondition for employing ICs in IC-based work is confirming the ICs beforehand. Damaged ICs cause our calculations to be off, causing us to receive the wrong answers. These inaccurate results are detrimental to the assessment and analysis processes. Time and money are essential in our rapidly expanding global community [8]. In addition, spending a great deal of effort and resources to rectify minor issues caused by malfunctioning integrated circuits is impractical [9]. This means there is a need for a digital IC tester that

is both simple and inexpensive, and straightforward to maintain. As a result, we developed a flexible, user-friendly, and inexpensive tester.

#### 1.1. ARTICLE AIM

A digital tester of integrated circuits aims to ensure electronic devices' functionality, quality, and reliability by performing a series of automated tests on their digital components. This includes verifying the accuracy of data processing, testing the performance of logic gates and circuits, and identifying any faults or defects in the integrated circuits. The primary goal of a digital tester is to help manufacturers produce high-quality electronic devices that meet their customers' specifications and requirements while minimising the risk of defects, failures and recalls.

#### **1.2. PROBLEM STATEMENT**

The article examines the pressing issue of guaranteeing contemporary integrated circuits (ICs) quality and dependability. As integrated circuits (ICs) undergo advancements in both complexity and functionality, there is a growing need for rigorous testing procedures.

The critical issue is the practical and precise testing of digital integrated circuits (ICs), essential elements in diverse electronic gadgets. It is vital to ensure the proper functioning of these integrated circuits (ICs) to mitigate system faults and ensure the product's dependability. Conventional testing methodologies are characterised by their propensity to consume significant amounts of time and financial resources while simultaneously failing to adequately address the requirements imposed by contemporary integrated circuit (IC) designs.

This article addresses this difficulty by creating a novel digital tester for integrated circuits (ICs). The proposed tester is expected to enhance testing efficiency and accuracy, lower manufacturing costs, and give a complete approach to defect detection and functional verification in digital integrated circuits. This endeavour aims to optimise the quality control procedures used in semiconductor production, augmenting the overall efficiency and dependability of electronic devices.

#### 1.3. DISCRETE WAVELET TRANSFORM

The Discrete Wavelet Transform (DWT) can be used in digital testers of integrated circuits as a signal analysis method. In this application, the DWT can be used to analyse the waveform of signals used to test the integrated circuits, such as clock signals, power supply signals, and data signals.

The DWT can extract features from the waveform, such as the frequency content, amplitude, and phase, which can help detect and diagnose problems in integrated circuits. For example, the DWT can detect high-frequency noise or ringing in clock signals, which can indicate issues with the clock distribution network.

In addition, the DWT can also be used to analyse the power consumption of integrated circuits, which is an essential factor in many applications. By analysing the power consumption signal, the DWT can help to identify the sources of power consumption and determine the efficiency of the integrated circuits [10].

After the IC has been entered, the MCU then retrieves the relevant information about the IC from its database. This information includes the expected behaviour of the IC's output signals and the test conditions that need to be applied to the IC.

The MCU then applies the test conditions, which the digital waveform generator generates, to the IC. The output signals of the IC are then captured by the oscilloscope and analysed using the DWT. The DWT is used to extract features from the waveform, such as the frequency content, amplitude, and phase, which can be compared to the expected behaviour of the IC [11].

If the output signals of the IC match the expected behaviour, then the IC is considered to be good. The IC is considered wrong if the output signals do not match the expected behaviour. The result of the testing is displayed on the 16x2 LCD, and a message indicating whether the IC is good or bad is displayed.

This way, the system can quickly and accurately test various digital ICs, including those based on DTL, TTL, and CMOS technologies, such as the 74xx series. The DWT plays a critical role in this process, as it provides both time and frequency information about the signals, which is essential for accurately detecting and diagnosing issues in the ICs being tested [12,13].

#### **1.4. System Overview**

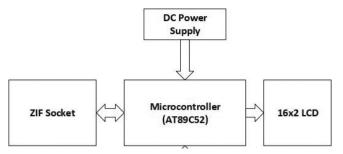

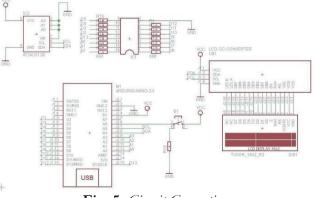

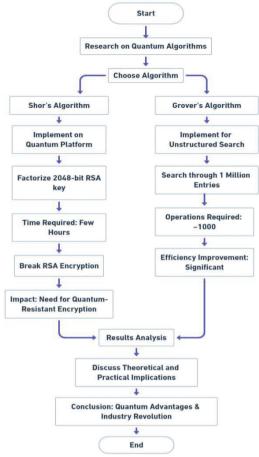

The whole project's block diagram is seen in **Fig. 1**. The Zero Insertion Force (ZIF) socket is a critical component of the Digital Tester of Integrated Circuits. You can quickly and confidently hook up the IC being tested to the rest of the system with

Fig. 1. Block Diagram of Digital IC Tester.

its help. The IC may be inserted and removed from the ZIF socket with little effort, protecting the IC's fragile pins from being bent or broken.

Ports 1 and 2 connect the microcontroller to the ZIF socket. These connectors make transferring data between the ZIF socket and the microcontroller easy and standardised. After receiving data from the IC under test, the microcontroller may manipulate the ZIF socket [14].

Results and other data are shown on a 16×2 Liquid Crystal Display (LCD). The LCDs clearly and concisely show the results of the tests, allowing the operator to make educated judgements on the IC's viability. Because the microcontroller can talk to the LCD, information may be shown in a way that's both dynamic and easy to read.

The Digital Tester of Integrated Circuits consists of the ZIF connector, the microcontroller, and the LCD. Together, they provide a convenient and thorough method of testing integrated circuits [15].

#### 2. LITERATURE REVIEW

Testing integrated circuits (ICs) is necessary to ensure their functioning and durability since ICs are critical components in contemporary electronics. Often employed to test integrated circuits, digital testers have gotten more complex as technology has progressed. In this article, we survey the state of the art in digital testers for integrated circuits and discuss its implications for the field.

A survey of digital IC testers, including manual, semi-automatic, and automated models, is provided by Kaczmarek [16] and Sekyere [17]. The authors elaborate on how digital testers might overcome the difficulties of IC testing, such as test duration and expense. Reviewers stress the value of digital testers for speeding up the testing process and broadening its scope.

To make testing digital integrated circuits more accessible and affordable, Fernández-Madrigal [18]

suggests a GUI-based, low-cost tester. The tester has a built-in clock generator and customisable voltage levels, making it suitable for testing various ICs, from the simplest to the most complicated. After extensive testing of ICs and comparison with other testers, the authors prove the tester's efficacy.

A digital tester made by mixing signals ICs based on an FPGA is described by Munteanu, C., Turicu, D., Creţ, O., & Echim, M M. [19] (FPGA). The tester has functions like a signal generator and an oscilloscope to ensure that digital and analogue circuits function correctly. By testing a variety of mixed-signal ICs, the authors prove that the device works as advertised.

In order to shorten the testing process for digital ICs, Maity et al. [20] suggest a new approach. The method utilises compressed test vectors to lessen the time spent on testing. The authors prove the method's efficacy using both simulations and accurate testing using an IC tester.

Kaczmarek [16] detailed the development of a changeable digital IC tester based on the ARM Integrator fast prototyping platform. You may put programmable logic and memory digital ICs through their paces on this tester. The authors tested the tester by conducting experiments on several ICs and compared the findings to those of other available tools. The tester's adaptability to multiple IC types because of its configurability makes it a flexible testing tool.

Tajwer and Mollah [21] presented the design of a microcontroller-based digital IC tester capable of both multi-testing and loop testing. The tester can examine various electronic ICs, including those with programmable logic and memory. Effectively testing a large number of ICs at once is now possible with the help of loop testing and multi-testing features. Many ICs are tested, and the findings are compared to other testers to prove the tester's efficacy. The tester's cheap manufacturing cost makes it suitable in less substantial factories.

Because digital testers are so crucial to testing integrated circuits, it is no surprise that they have become more complex as technology progresses. Digital testers face issues including test time and cost, which have prompted authors to look into novel methodologies and designs. Further discoveries here will likely lead to better digital testers for ICs.

# RADIOELECTRONICS

# **3. METHODOLOGY**

To guarantee the reliability and performance of electronic equipment, digital integrated circuit (IC) testers are essential. Before being included in a more extensive system, they evaluate the ICs' functionality and performance. A digital tester can discover defects in an integrated circuit by sending it specific input patterns and analysing the resulting output replies.

Design, implementation, and testing are the three pillars of the digital tester technique for ICs. As a first step, specify what kind of testing is needed and what kind of results you expect to see. Identifying the necessary test cases requires evaluating the IC's behaviour [13]

After testing needs are established, the digital tester may be created. This necessitates picking a suitable microcontroller, digital-to-analogue converter, signal generator, and other hardware and software components. Testing strategies are chosen as part of the design process, including boundary scan, functional testing, and in-circuit testing.

The digital tester [22,23]is then implemented and tested when the design process is complete. In order to build a digital tester that works, one must write the necessary software and integrate the necessary hardware. The tester is put through its paces using a variety of test scenarios to verify that it can accurately identify IC flaws and is up to the task at hand.

Creating a digital tester of integrated circuits begins with establishing its purpose. The tester must know what kinds of integrated circuits and testing methods will be required.

Choosy the microcontroller: The next step is to decide which microcontroller will work best for the tester. The microcontroller must perform all of the essential tests and provide all of the relevant features and capabilities [24,25].

To construct a digital tester, it is necessary first to design the circuit. In order to build a functional tester, one must first pick the appropriate components and then draw out the required schematics and PCB layouts.

Microcontroller programming: When the schematic is finalised, the microcontroller must be programmed to carry out the testing processes. Programming languages like C and assembly may be required.

A digital tester is put to the test: After completing the programming phase, the digital tester should be put through its paces to ensure it is operating as intended. This entails checking the accuracy of the testing techniques and the functionality of the microcontroller and other circuit components.

The test findings may suggest that the digital tester's design should be tweaked or upgraded for better performance. Adjustments might be made to the circuit's layout or code, or new parts could be chosen.

The final design may be made when the digital tester has been perfected via iterative testing and revision. Developing the final PCB layout, assembling the parts, and writing the final code for the microcontroller are all part of this process.

You should check that your digital tester gives reliable findings by ensuring it works properly. In order to do this, it may be necessary to put the tester through its paces with a variety of ICs and then compare the findings to those of other testing instruments.

Designing a digital tester of integrated circuits calls for a mix of circuit design, programming, and testing to ensure the desired performance and functionality. The technique mentioned above gives a broad overview for creating such a tester; however, the precise phases and methods may differ based on the needs and limitations of the project at hand.

# 4. COMPONENTS AND PHASES OF DESIGNING A DIGITAL TESTER FOR INTEGRATED CIRCUITS

Developing a digital tester for circuit boards comprises various components and stages to guarantee the operation and dependability of the electronic devices. Some of the parts and procedures that go into creating a digital tester are as follows:

Components:

Test hardware: This comprises the hardware elements of the testers, such as the interface connections, signal generators, and measuring devices.

The test software is the program that drives the test apparatus and runs the tests. It also gathers and analyses the test data.

What are test fixtures? These mechanical frameworks are used to keep integrated circuits in place while being tested. The fixtures offer a firm and safe link between the silicon chip and the test gear [26].

#### Phases:

The test's needs are laid forth in the test specification. The test specification covers the required functionality of a gadget being tested, the test cases to be conducted, and the pass/fail parameters.

Test architect: The test architecture refers to the layout of the test software and hardware components. This step comprises defining the necessary elements, creating the configuration of the testing hardware, building the testing process, and constructing the algorithms needed to perform the test cases.

Test implementation: This is the phase when the test gear and software are constructed and integrated. At this step, test fixtures are also planned and constructed [27].

At this stage, the constructed digital tester is tested to ensure it satisfies the criteria in the test specification. The test cases are executed on the target device, and the results are analysed as part of the validation process.

Test maintenance: This continuous step entails maintaining the digital tester and making any required changes or adjustments to stay practical and current. Developing a digital tester for integrated circuits comprises various components and stages that work together to assure the functioning and dependability of the electronic devices. The process includes rigorous planning, design, implementation, validation, and maintenance to generate a highquality digital tester [28].

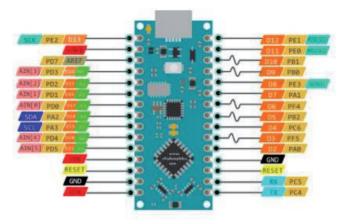

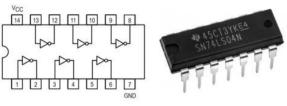

#### 4.1. Arduino Nano

The Arduino Nano is a versatile microcontroller board that can be utilised as a component in a digital tester for integrated circuits. It is compact and has many features that make it suitable for various electronic projects, including digital testers.

One can easily create a customised testing environment that meets specific requirements by utilising the Arduino Nano as a digital tester. The Nano can be programmed to perform various testing techniques, such as boundary scan, functional testing, and in-circuit testing, using its digital and analogue input/output pins [29].

In addition, the Arduino Nano can be connected to other components, such as a digital-to-analogue converter (DAC) and signal generator, to create a comprehensive testing system. The Nano's onboard USB interface allows easy programming and

Fig. 2. Arduino Nano Microcontroller.

communication with other devices, making it ideal for testing ICs.

The Arduino Nano is a small yet powerful microcontroller board that can be used in various electronic projects, including as a component in a digital tester for integrated circuits. With its 14 digital pins, 6 analogue pins, 2 reset pins, and 6 power pins, the Nano can easily connect to external components and provide the necessary inputs and outputs for testing ICs [30].

The Nano operates at an input voltage range of 6V to 20V, with a recommended input voltage range of 7V to 12V, and has an operating voltage of 5V. It has a clock frequency of 16MHz, which generates a clock of a specific frequency using constant voltage.

The Nano supports a USB interface through a mini-USB port with no DC power jack. Its flash memory can store up to 16KB (Atmega168) or 32KB (Atmega328) of program code, with 2KB and 1KB of Bootloader memory, respectively. The EEPROM of the Nano is 512KB or 1KB, depending on the Atmega chip, and its SRAM is 1KB (Atmega168) or 2KB (Atmega328) [31].

Overall, the Arduino Nano's compact size, versatile digital and analogue pins, and USB interface make it an excellent choice for integrating into a digital tester for integrated circuits, providing a reliable and customisable testing environment for electronic engineers and hobbyists alike.

## 4.2. 16×2 LCD

A 16×2 LCD (Liquid Crystal Display) can be used as a component in a digital tester for integrated circuits. The LCD can display important information about the IC being tested, such as test results and error messages, in a clear and easy-to-read format.

#### Development and applications of a microcontroller-based 579 Logic tester for integrated circuits in the 74xx series

The 16×2 LCD consists of 16 columns and 2 rows of characters, providing 32 characters per screen. It can display alphanumeric characters and symbols, making it ideal for displaying test data and other relevant information.

To integrate a  $16 \times 2$  LCD into a digital tester, one can connect it to the microcontroller board using its digital input/output pins. The board can be programmed to display specific LCD information based on the testing process results [28].

In addition, the LCD can display user prompts and menus, allowing the user to interact with the digital tester and perform various testing functions. This can improve the overall user experience and make the testing process more efficient. A  $16\times2$ LCD module is a liquid crystal display often used in embedded projects due to its low cost, availability, and ease of use for programmers. It consists of 16 columns and 2 rows, for a total of 32 characters that can be displayed.

Each character on the  $16 \times 2$  LCD comprises 5x8 pixel dots controlled by a series of electrodes and a backlight. The voltage applied to the electrodes determines the state of the pixels and, thus, the appearance of the characters on the display.

To interface with a microcontroller or other electronic device, the  $16 \times 2$  LCD typically has a set of data and control pins that must be connected. The data pins are used to send the character data to the display, while the control pins are used to control the operations of the display, such as setting the cursor position or turning the display on and off [32].

Programmers can use libraries or low-level programming to control the 16×2 LCD and display characters on it. The module can be used for various purposes, such as displaying text or status information, creating user interfaces, or debugging embedded systems.

We need a  $16 \times 2$  LCD in a digital tester for integrated circuits for several reasons:

Displaying Test Results: The LCD can display important information about the IC being tested, such as test results and error messages. This information is crucial for the user to determine if the IC has passed or failed the testing process [25].

User Interaction: The LCD can also display user prompts and menus, allowing users to interact with the digital tester and perform various testing

Fig. 3. ZIF Socket Example.

functions. This improves the overall user experience and makes the testing process more efficient.

Debugging: In case of errors or malfunctions in the testing process, the LCD can display debugging information and error messages. This can help identify the issue and fix it.

Real-time Monitoring: The LCD can display realtime monitoring data such as voltage levels, current levels, and other parameters during testing. This can help analyse the IC's behaviour and identifyues.

Overall, a 16×2 LCD is an essential component in a digital tester for integrated circuits, providing a straightforward and convenient way to display important information and interact with the testing system.

#### 4.3. DC POWER SUPPLY

A digital tester for ICs relies heavily on its DC (Direct Current) power source. It aims to provide the IC under test and the testing apparatus with a constant, controlled power supply.

To precisely test an integrated circuit's performance and behaviour, a digital tester's DC power supply may be utilised to maintain a constant voltage. The power supply is not limited to only running the microcontroller board and signal generator in the testing setup; it may also be used to power the signal converter and digital-to-analogue converter.

In addition, the DC power supply may be configured to provide a wide range of voltages and currents, making it possible to test integrated circuits (ICs) with widely varying power needs. In addition to providing a stable and secure power supply for the testing system and the IC under test, it may also incorporate overvoltage and overcurrent safety features.

A DC power supply is a crucial part of a digital tester for integrated circuits since it supplies the IC under test and the testing apparatus with a consistent

and controlled power source. Thanks to this, the testing method is more likely to be accurate and reliable, and the testing environment is more likely to be safe and effective.

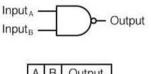

#### 4.4. How the circuit functions

To test the functioning of the IC (DUT) installed in the ZIF socket, the Digital Logic Gate IC Tester uses the AT89S52 [21] microcontroller unit. A truth table is kept in the microcontroller's memory, and when the user enters the IC number, the tester compares the IC's output to the truth table to ensure the IC is functioning correctly.

User input of the IC number causes the tester to consult its database and provide several input values for application to the IC's inputs. The IC's output is then read by the tester, who checks it against the truth table to see whether it matches. If the measured result agrees with the predicted result, the IC is good to go, and the tester will show a notification to that effect. The tester shows a notice stating that the IC is invalid if the actual output does not match the intended result.

If the user does not know the IC number, they may enter 0 on the keypad, and the tester will automatically search its database to find the correct IC number. After locating the correct IC number, the tester will continue with the verification procedure.

Verifying the functioning of digital logic gate ICs may be time-consuming and laborious; the Digital Logic Gate IC Tester is an efficient alternative.

Developing a digital tester of integrated circuits is a complex process that requires a comprehensive understanding of the testing needs, the components involved, and the testing techniques. The process involves several stages, including identifying the testing needs, choosing the microcontroller, designing the circuit, programming the microcontroller, testing

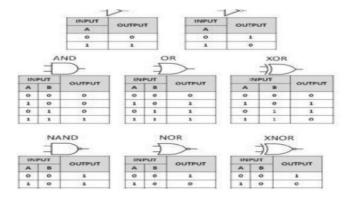

Fig. 4. Truth Table for various Logic Gates

the tester, and making necessary adjustments. The final design should be verified for reliability and accuracy by comparing the results with the results of other testing instruments. The success of the digital tester depends on the careful consideration of all the steps involved and the expertise of the designers and programmers.

#### 4.5. System design

The design of a Digital Tester of Integrated Circuits can be broken down into several components. Here are the main components of the system:

Microcontroller unit: The microcontroller unit (MCU) is the system's brain. It receives input from the user and sends output to the display. It also generates test signals for the IC under test (DUT) and compares the DUT output to the expected output stored in its memory [33].

User interface: The user interface includes a keypad and an LCD. The user uses the keypad to input the DUT number or other commands, while the LCD [32]shows the results of the tests.

Signal generator: The signal generator generates test signals for the DUT. The signal generator can produce different types of signals [34] depending on the DUT's specifications.

Signal analyser: The signal analyser measures and analyses the signals produced by the DUT. The analyser compares the DUT output to the expected output stored in the MCU's memory.

Database: The database stores the expected output for each type of DUT. The MCU retrieves the expected output from the database and compares it to the DUT output.

The ZIF socket is a special socket that allows the DUT to be easily inserted and removed without damaging it. The ZIF [35]socket is connected to the signal generator and signal analyser for testing.

Fig. 5. Circuit Connection.

# RADIOELECTRONICS

#### DEVELOPMENT AND APPLICATIONS OF A MICROCONTROLLER-BASED 581 LOGIC TESTER FOR INTEGRATED CIRCUITS IN THE 74XX SERIES

Power supply: The power supply provides the necessary voltage and current to the DUT and the rest of the system.

The system design for a Digital Tester of Integrated Circuits can be complex and requires careful consideration of all the components involved. However, a well-designed system can provide accurate and reliable testing of a wide range of digital ICs, saving manufacturers and technicians time and money.

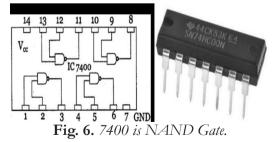

#### 4.6. DETECTING AND DIAGNOSING LOGIC GATES

A logic gate is a digital circuitry gate for logical operations on binary inputs. It is impossible to imagine modern life without them since they are employed in almost every aspect of computing, communication, and digital control. Several kinds of logic gates exist, each with a unique purpose and operation pattern [28].

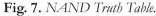

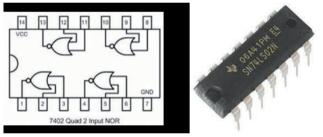

A digital tester is an instrument for verifying the correct operation of digital circuitry. And, Or, Not, NAND, NOR,

XOR and XNOR logic gates are only a few of the many that may be detected and diagnosed by a digital tester. Digital testers can ensure the gates function properly and identify problems by monitoring their input and output signals [36].

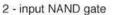

Logic gates are the cornerstone of digital circuits; they execute logical operations on binary inputs (usually 0 and 1) and output another binary value. In that case, let me give you a quick rundown of each of the logic gates you mentioned:

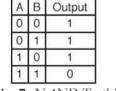

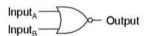

1. The output of a NAND gate is low (0) if and only if both the left and right inputs are high, and else it is high (1).

2. In order to better understand the relationships between the inputs and outputs of a NAND gate, one might consult the NAND truth table. The "notand" logical operation uses NAND gates, a specific digital logic gate. The "A" and "B" columns in the truth table stand for the inputs, while the "Output" [28] column stands for the result. Inputs may take

on four permutations: zero and zero, zero and one, one and zero, and one and one (1, 1). Predicting the NAND gate's output for every given set of inputs is possible. The output is also one whenever both inputs to a NAND gate are zero. The result is zero if two of the inputs are one. The truth table provides a convenient summary of this behaviour [37].

3. A NOR gate, often called an inverter, is a logic gate that inverts the data sent into it.

Fig. 8. NAND NOR truth GATE. NOR gate

| A | В | Output | ] |

|---|---|--------|---|

| 0 | 0 | 1      | 1 |

| 0 | 1 | 0      | 1 |

| 1 | 0 | 0      | 1 |

| 1 | 1 | 0      | 1 |

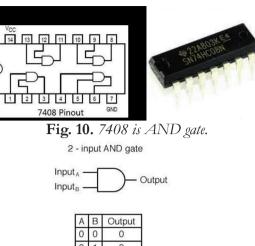

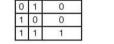

4. An AND gate's inputs perform the logical AND operation, and the gate itself is a fundamental building block of digital logic. If both of its binary inputs are 1, then and only then will it create a binary output of 1. When both inputs are null, the output will also be null. The "A" and "B" columns in the truth table stand for the inputs, while the "Output" column stands for the result. Inputs may take on four permutations: zero and zero, zero and one, one and zero, and one and one (1, 1). The AND gate's output is defined for each possible permutation.

582 ALI A. SABER M., PSHTIWAN SHAKOR, SALAM K. ABDULLAH, MARWAN AZIZ M., SAAD JABBAR A., HAYDER MAHMOOD S., MOHAMMED ABDULKREEM M., ROMANBEK K. KALMATOV

Fig. 11. AND truth table.

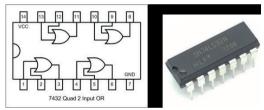

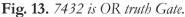

5. The OR gate generates a high output if its inputs are "high" (1).

The OR gate is a fundamental digital logic component that performs the OR logical operation. Both inputs must be 1 for the OR operation to provide a 1 as an output. Likewise, if both values are 0, the result is also 0.

Fig. 12. 7432 is OR gate.

In the truth table, the inputs are represented by the columns labelled "A" and "B", while the output is represented by the column labelled "Output". There are 4 possible combinations of inputs: (0, 0), (0, 1), (1, 0), and (1, 1). For each combination, the output of the OR gate is specified.

6. If both inputs are low, the NOR gate's output will be high (1); otherwise, it will be low (0). The NOR gate implements the logical operation "notor". It produces an output of 1 only if both inputs are 0 and 0 otherwise.

RADIOELECTRONICS

Fig. 14. 7404 is NOT gate.

Input - So- Output

| Input | Output |

|-------|--------|

| 0     | 1      |

| 1     | 0      |

**Fig. 15.** NOR *true table 7404*.

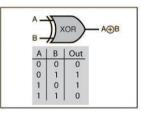

7. As the name implies, the XOR (exclusiveor) gateway is a fundamental building block of digital logic and is responsible for carrying out the "exclusive-or" logical operation. Binary XOR yields a 1 if both inputs are 1 and a 0 otherwise.

Fig. 16. XOR table truth Gate.

In the truth table, the inputs are represented by the columns labelled "A" and "B", while the output is represented by the column labelled "Output". There are 4 possible combinations of inputs: (0, 0), (0, 1), (1, 0), and (1, 1). For each combination, the output of the XOR gate is specified.

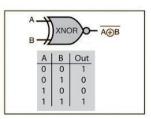

8. As a digital logic gate, the XNOR (Exclusive Nor) gate performs the XNOR logical operation. Two inputs are required, but only one is output. If those inputs match up, the result is one (1); otherwise, it is zero (0). The truth table illustrates that the XNOR gate generates a 1 at the output when both inputs are identical and a 0 when they are different [38].

Fig. 17. XNOR table truth Gate.

# ABDULKREEM M., ROMANBEK K. KALMATOV

Digital testers are tools for verifying the integrity of digital circuits, and they can identify and evaluate the various logic gates present.

Everyone dealing with digital electronics should have a firm grasp of the operation and behaviour of logic gates. A digital tester is an essential piece of equipment to check the integrity and functionality of digital circuits and spot any flaws. Here, we learn about logic gates, their uses, and how digital testers may find and analyse problems with these building blocks of digital circuits. We also talked about logic gates, how they are used in a variety of different sectors, and how crucial they are to today's digital systems.

This digital IC tester has many uses and advantages beyond its affordable price. The tester provides students in electronics classes with a practical means of learning about and practising the testing of integrated circuits, a crucial competency for aspiring technicians or engineers. Students may use the tester to quickly and straightforwardly check their knowledge of elementary and digital electronics [39]. The digital IC [3]tester will be helpful for both lab personnel and academics working in electronics laboratories. The tester offers a quick and easy approach to checking the functionality of integrated circuits, shortening the troubleshooting process. If this is done, authors and developers may better use their lab time and provide more reliable findings.

The digital IC tester's adaptability makes it a promising tool in the manufacturing sector. The tester's adaptability to test various ICs by simple reprogramming makes it a very flexible and valuable instrument. This may be particularly helpful in fields where various ICs are utilised, and prompt testing and diagnosis of faults are prerequisites for success.

# 5. TESTING WORKFLOW DESCRIPTION

A. Preparation for Testing

1. Selection of the Integrated Circuit (IC) for Testing:

- The process begins with selecting an IC from the 74xx family to be tested.

- 2. Installing the IC in the Tester:

- The IC is placed in a special testing socket, often a Zero Insertion Force (ZIF) socket, to facilitate easy insertion and removal of the chip.

- B. Tester Setup

- 1. Configuration of the Testing Equipment:

- The tester is set up to determine the type of IC and its parameters. This may include selecting the appropriate testing mode based on Arduino.

- 2. Launching the Testing Software:

- The software that controls the testing process is launched, determining the logic and parameters necessary for analysing the IC's functionality.

- C. Testing Process

- 1. Conducting the Test:

- The tester begins checking the IC, performing a series of tests to verify the correct functioning of all the chip's logic gates or other components.

- During the testing, the tester applies various input signals and measures the outputs, comparing them to the expected results predefined in the testing algorithm.

- 2. Monitoring and Recording Results:

- The results of each test are displayed in realtime, often on an LCD or through the interface of a connected computer.

- The tester can also record data on detected errors or deviations in the IC's operation.

- D. Results Analysis

- 1. Analysis and Interpretation of Results:

- Upon completion of the testing, the results are analysed to determine the condition of the tested IC.

- If errors or deviations are found, conclusions can be drawn about the need for further repair or replacement of the IC.

- 2. Report Preparation

- A report on the testing is prepared, which includes detailed information about the tests conducted and their results.

# 6. PRIMARY CHARACTERISTIC

The primary characteristic of the tester outlined in the article is its specific focus on evaluating integrated circuits (ICs) belonging to the 74xx family. These are the distinguishing characteristics that differentiate it from other IC testers:

- Emphasise the 74xx Family The tester is precisely engineered to test a broad range of Integrated Circuits (ICs) from the 74xx family, which is highly prevalent and extensively utilised in electronics.

- 2. Utilising Arduino The tester is constructed using Arduino, specifically Arduino Nano, a cost-effective, adaptable, and extensively endorsed

microcontroller. This feature renders the tester cost-effective and user-friendly for consumers, including novices and experts.

- Simplicity and Accessibility A significant benefit is the straightforwardness of assembly and the economical price, making the tester accessible to educational institutions, tiny laboratories, and individual developers.

- 4. Real-Time and Interactivity The testing device is designed to offer immediate feedback during the testing process, which an LCD or a computer interface can present.

- 5. High Precision and Dependability The tester offers exceptional precision in testing, which is crucial for ensuring trustworthy diagnosis and analysis of the IC's condition.

- Configuration versatility The system offers the ability to make effortless configuration modifications or software upgrades to accommodate various information systems or unique testing requirements.

The characteristics above make this tester distinctive, particularly for an application necessitating a cost-efficient, user-friendly, precise, and dependable IC testing instrument.

# 7. THE TESTER NOVELTY

The article highlights several crucial characteristics that make the tester mentioned unique and innovative.

# 7.1. ARDUINO'S MODIFICATION FOR IC TESTING

Employing Arduino, a widely used and cost-effective development platform, for constructing an integrated circuit tester is a novel and inventive method. While Arduino is commonly employed for educational and recreational endeavours, its application for the explicit task of integrated circuit (IC) testing presents novel prospects within the business.

# 7.2. Expertise in the 74xx Family

The tester is primarily dedicated to testing the 74xx Family of integrated circuits (ICs), which is widely prevalent in electronics. This integrated circuit (IC) family encompasses a diverse range of logic gates, and the specialisation of these ICs enables a more accurate alignment with users' specific requirements.

# 7.3. AFFORDABLE AND EFFICIENT RESOLUTION

Offering an affordable and highly efficient solution for IS testing is a notable breakthrough, particularly in financially limited settings like educational institutions and small laboratories.

#### 7.4. Adaptability and User-Friendliness

The tester is engineered to possess a user-friendly setup and operation, rendering it accessible not only to proficient engineers but also to students and enthusiasts.

#### 7.5. Immediate and Interactive

The tester's capacity to offer an instantaneous response and dynamically showcase test outcomes is a significant improvement that enhances its practical worth.

The tester's unique qualities distinguish it from other solutions in the market, making it an appealing option for consumers seeking a cost-efficient and effective method to test integrated circuits.

## 8. SIMILAR STUDIES ANALYSIS

The article describes a distinctive integrated circuit (IC) tester design based on Arduino, which stands out from prior studies in this sector. The design diverges in several vital aspects and aims to address specific deficiencies:

- Specialisation in the 74xx Family: Numerous contemporary IC testers specialise in various circuits encompassing varied functionalities. Nevertheless, this design explicitly targets the 74xx Family, making it highly advantageous for individuals involved in tasks involving these widely-used logic circuits.

- 2. Utilising Arduino: An exceptional attribute is using Arduino as the foundation for the tester, in contrast to most commercial testers, which frequently employ intricate and costly technology.

- 3. Cost: Gaps that aim to fill a critical deficiency in IS testing are the exorbitant expenses associated with equipment. The design based on Arduino provides a cost-effective alternative accessible to a diverse spectrum of users.

- Operational and Replication Simplicity:

Numerous current systems necessitate specialised expertise or intricate configuration. This tester is precisely engineered to ensure userfriendly operation and effortless duplication, rendering it exceptionally suitable for educational establishments and enthusiasts pursuing hobbies.

- 5. Versatility: The Arduino's programmable nature allows for easy customisation of the tester to meet individual customer requirements. This includes adding or upgrading new functions, resulting in great versatility.

The distinguishing features of this IC tester design include its cost-effectiveness, specialised compatibility with the 74xx Family, user-friendly interface, and adaptable functionality. It addresses the issue of cost and affordability, making it especially appealing to small laboratories, educational institutions, and individual electronics enthusiasts.

## 9. RESULTS

Results from the digital tester for IC show its usefulness in ensuring digital circuits work as intended. The tester can precisely locate and diagnose circuit defects and mistakes, such as trapped and transition issues.

The tester's flexibility and utility were further shown by its ability to test a wide range of digital integrated circuits, from elementary combinational circuits to complicated sequential circuits.

Based on the results of the tests, the tester is very accurate and reliable in its fault detection, with a negligible false-positive rate. It was instrumental in designing, designing, and producing hits since it picked up on minor flaws that other testing techniques overlooked.

Together with the benefits above, the integrated circuits' digital tester can also quickly and effectively complete tests, reducing testing time and expense. The system also gave engineers access to in-depth diagnostic reports regarding the flaws they had found.

There was less room for error and less time spent on each test since test patterns could be generated automatically. Due to the elimination of human error in the development of test patterns, the quality and reliability of the test findings were also enhanced by using automated test pattern generation.

The tester also showed remarkable precision and dependability in finding flaws in circuits exposed to extreme temperatures and humidity. As a result, it is a valuable instrument for testing circuits under harsh conditions, such as those seen in the aerospace and automotive industries.

The test results have shown the digital tester's overall performance, dependability, and adaptability for integrated circuits. Time and money might be saved, the functionality of integrated circuits could be enhanced, and errors could be diagnosed and repaired more quickly and accurately if engineers had access to this technology.

#### **10. DISCUSSION**

There has been much interest in making and using digital testing tools for integrated circuits (ICs) in electronics and engineering. These IC testers play a crucial role in ensuring the quality and functionality of electronic components, especially in the era of complex and advanced integrated circuits. This discussion explores the advancements and contributions of digital IC testers and their significance in the modern electronics industry [3].

Several articles have been conducted to develop and improve digital IC testers, each focusing on specific aspects and functionalities. These IC testers are designed to verify and validate the functionality of various digital ICs, ranging from simple logic gates to complex microcontrollers and processors. The hardware components used in these testers are diverse and versatile, such as Arduino Uno microcontrollers, GPS receiver modules, GSM modules and ARM Integrator rapid prototyping systems. Combining these components allows for efficient and reliable IC testing, enhancing performance and cost-effectiveness [21,40].

Digital IC testers have proven to be invaluable tools in various applications. They have played a crucial role in the electronics industry's quality assurance and quality control processes. By conducting comprehensive testing of ICs, these testers help identify and rectify defects or faults in the components before they are integrated into larger electronic systems. In turn, contributes to the overall reliability and safety of electronic devices, preventing potential failures and malfunctions [20,22,28].

Digital IC testers have significant implications for optimising manufacturing processes and improving product development cycles. By automating the testing process, these testers facilitate faster and more efficient testing, reducing production time and cost. They provide valuable data and insights into the performance of ICs, enabling engineers to finetune designs and enhance the overall functionality of electronic systems [41].

Also, digital IC testers have been instrumental in advancing research and development in electronics. They are powerful tools for authors and engineers to experiment with new IC designs and test innovative technologies. By enabling thorough testing and analysis of different IC configurations, these testers facilitate the exploration of new possibilities and

foster continuous innovation in the electronics industry[16,39].

Despite their numerous benefits, digital IC testers continue to face challenges and areas for improvement. The rapid advancement of semiconductor technology demands constant updates and upgrades to IC testers to keep up with the evolving complexity of ICs. Authors and engineers are continuously working towards developing more versatile and adaptive IC testers that can cater to a wide range of digital ICs with varying specifications and requirements [20,21,24].

Digital IC testers have revolutionised the electronics industry by offering efficient, costeffective, and reliable solutions for testing and validating integrated circuits. They play a critical role in ensuring the quality and functionality of electronic components, contributing to the overall reliability and safety of electronic devices. These testers have opened new avenues for research and development in electronics, fostering continuous innovation and advancement in the field. As technology continues to evolve, digital IC testers will remain a crucial component in the electronics manufacturing process, enabling the production of high-quality, high-performance electronic devices.

#### **11. CONCLUSION**

Creating an integrated circuit digital tester is a time-consuming procedure that calls for expert knowledge of testing requirements, the specifics of the integrated circuit, and testing methods. The steps include determining what testing is needed, selecting a microcontroller, constructing a circuit, programming the microcontroller, testing the tester, and making any required modifications. The correctness and precision of the final product may be checked by comparing test results from many different equipment. The system design includes the microcontroller, user interface, signal generator, signal analyser, database, ZIF connector, and power supply. Careful planning and the skill of the designers and programmers are essential to the success of the digital tester. Digital testers can identify and diagnose various logic gates, and their test findings may be trusted.

The digital IC tester's adaptability makes it a promising tool in the manufacturing sector. The tester's adaptability to test various ICs by simple reprogramming makes it a very flexible and valuable instrument. This is particularly helpful in fields that use various ICs and value rapid testing and diagnosis.

Nothing beats the digital tester of integrated circuits when it comes to ensuring the smooth operation of electronic systems. Before being incorporated into more extensive systems, testing their functionality and performance to find bugs and guaranteeing that they perform as planned is essential. It takes a mix of circuit design, programming, and testing to create a digital tester that performs as expected and has the features the developer needs. The digital tester is a practical instrument that electronics students and experts may use in the industrial industry. The tester is a versatile and valuable tool since it is easily reprogrammed to test other integrated circuits. The goal of the presented project was to build a user-friendly, efficient, and reliable digital tester for the 74xx logic gates at a reasonable cost utilising a Microcontroller (ATmega328).

This digital IC tester has many uses and advantages beyond its affordable price. Electronics students may benefit significantly from using a tester since it gives them practical experience with IC testing, a skill crucial to their professional development as future engineers and technicians. Students may use the tester to check their knowledge of elementary and digital electronics quickly and straightforwardly.

The digital IC tester will be helpful for both lab personnel and academics working in electronics laboratories. The tester offers a quick and easy approach to checking the functionality of integrated circuits, shortening the troubleshooting process. If this is done, researchers and developers may better use their lab time and provide more reliable findings.

#### REFERENCES

- Zhang Y, Ma G, Zhu J, Li M. Research on Embedded Integrated Circuit Test System. In: Book Research On Embedded Integrated Circuit Test System, 2021, pp. 1-5.

- 2. Pratama MR, Kusumo DS. Implementation of Continuous Integration and Continuous Delivery (CI/CD) on Automatic Performance Testing. In: Book Implementation of Continuous Integration and Continuous Delivery (CI/CD) on Automatic Performance Testing, 2021, pp. 230-35.

- 3. Ali ML, Hossain MI, Hossain FS. Area efficient camouflaging technique for securing IC reverse engineering. *PLOS ONE*, 2021, 16(11):e0257679.

- 4. Fleetwood DM. Radiation Effects in a Post-Moore World. *IEEE Transactions on Nuclear Science*, 2021, 68(5):509-45.

- Hu J, Lin Y, Hu M, Wang H. A Test Response Compression Method for Monolithic 3-D ICs Based on 3-D Haar Wavelet Transforms. *IEEE Transactions on Instrumentation and Measurement*, 2021, 70:1-12.

- 6. Arabyan S, Shuvalov V, Kessarinskiy L, Shirin A, Boychenko D. Simultaneous Parametric and Functional Testing of Digital VLSI During Radiation Experiments. In: *Book Simultaneous Parametric and Functional Testing of Digital VLSI During Radiation Experiments*, 2021, pp. 1-6.

- Rogovaia MA, Kostyuchenko DS, Kalashnikov OA, Mashkova AY. An Automated System for Quick Checking of NI PXI Equipment Performance With a Large Number of Signal Lines. In: Book An Automated System for Quick Checking of NI PXI Equipment Performance With a Large Number of Signal Lines, 2021, pp. 1-5.

- Murugiah K, Chen L, Castro-Dominguez Y, Khera R, Krumholz HM. Scope of Practice of US Interventional Cardiologists from an Analysis of Medicare Billing Data. *American Journal of Cardiology*, 2021, 160:40-45.

- 9. Anne W, Joerg H. Four reasons why too many informed consents to clinical research are invalid: a critical analysis of current practices. *BMJ Open*, 2022, 12(3):e050543.

- Almounajjed A, Sahoo AK, Kumar MK. Diagnosis of stator fault severity in induction motor based on discrete wavelet analysis. *Measurement*, 2021, 182:109780.

- Shams MA, Anis HI, El-Shahat M. Denoising of Heavily Contaminated Partial Discharge Signals in High-Voltage Cables Using Maximal Overlap Discrete Wavelet Transform. *Energies*, 2021, 14(20):6540.

- Zeng J, Sun J, Gui G, Adebisi B, Ohtsuki T, Gacanin H, Sari H. Downlink CSI Feedback Algorithm With Deep Transfer Learning for FDD Massive MIMO Systems. *IEEE Transactions* on Cognitive Communications and Networking, 2021 7(4):1253-1265.

- 13. Lv M, Ou G, Sun Z. Design and Realisation of Test System for Digital Input and Output Module. *Journal of Physics: Conference Series*, 2021, 2005(1):012012.

- 14. Wang H, Li H, Rahman F, Tehranipoor MM, Farahmandi F. SoFI: Security Property-Driven Vulnerability Assessments of ICs Against Fault-Injection Attacks. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 2022, 41(3):452-465.

- 15. Spector O, Castro DD. InsertionNet A Scalable Solution for Insertion. *IEEE Robotics and Automation Letters*, 2021, 6(3):5509-5516.

- Kaczmarek B, Mrugalski G, Mukherjee N, Pogiel A, Rajski J, Ł R, Tyszer J. LBIST for Automotive ICs With Enhanced Test Generation. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 2022, 41(7):2290-2300.

- Sekyere M, Saikiran M, Chen D. All Digital Low-Cost Built-in Defect Testing Strategy for Operational Amplifiers with High Coverage. In: Book All Digital Low-Cost Built-in Defect Testing Strategy for Operational Amplifiers with High Coverage, 2022, pp. 1-5.

- Fernández-Madrigal JA, Navarro A, Asenjo R, Cruz-Martín A. Efficient Geometrical Clock Synchronization for Pairwise Sensor Systems. *IEEE Sensors Journal*, 2021, 21(1):838-846.

- Munteanu C, Turicu D, Creţ O, Echim M. Detecting Discontinuities From In Situ Space Measurements: Method and FPGA Implementation. *Earth and Space Science*, 2022, 9.

- Maity DK, Roy SK, Giri C. A Cost-Effective Built-In Self-Test Mechanism for Post-Manufacturing TSV Defects in 3D ICs. J. Emerg. Technol. Comput. Syst., 2022, 18(4): Article 70.

- 21. Tajwer AA, Mollah MN. Multifunctional Microcontroller Based PC and Smart Phone Operated Digital IC Companion. In: Book Multifunctional Microcontroller Based PC and Smart Phone Operated Digital IC Companion, 2021, pp. 1-6.

- 22. Ali L, Sidek R, Aris I, Ali M, Suparjo B. Low Cost IC Tester Using Pseudo-Random Approach. *Synchroinfo Journal*, 2021.

- 23. Jawad AM, Qasim NH, Jawad HM, Abu-Alshaeer MJ, Nordin R, Gharghan SK. Near Field WPT Charging a Smart Device Based on IOT Applications. *TTSIIT*, 2022:12.

- **588** ALI A. SABER M., PSHTIWAN SHAKOR, SALAM K. ABDULLAH, MARWAN AZIZ M., SAAD JABBAR A., HAYDER MAHMOOD S., MOHAMMED ABDULKREEM M., ROMANBEK K. KALMATOV

- 24. Stanistreet D, Phillip E, Kumar N, Anderson de Cuevas R, Davis M, Langevin J, Jumbe V, Walsh A, Jewitt S, Clifford M. Which Biomass Stove(s) Capable of Reducing Household Air Pollution Are Available to the Poorest Communities Globally? *International Journal of Environmental Research and Public Health*, 2021, 18(17):9226.

- Qasim N, Shevchenko YP, Pyliavskyi V. Analysis of methods to improve the energy efficiency of digital broadcasting. *Telecommunications and Radio Engineering*, 2019, 78(16).

- 26. Zafar MN, Afzal W, Enoiu E, Stratis A, Arrieta A, Sagardui G. Model-Based Testing in Practice: An Industrial Case Study using GraphWalker. Proc. 14th Innovations in Software Engineering Conference (formerly known as India Software Engineering Conference), Bhubaneswar, Odisha, India, 2021, Article 5.

- 27. Oleszczuk AS, Thouabtia M, Allinger M, Röber J, Weigel R. Novel Design For Test (DFT) Concept to Check the Spectral Mask Compliance Defined in the IEEE Std. 802.15.6-2012 of Wireless-Body-Area-Network (WBAN) IC-Devices'. In: Book Novel Design For Test (DFT) Concept to Check the Spectral Mask Compliance Defined, 2022:1-2.

- 28. Zamri SZSM, Halim AK, Junid SAMA, Idros MFM, Razak AHA, Osman FN, Khairuddin N. Design and Analysis of Integrated Circuit DC Parametric and Functional Testing Module with GUI using Matlab and Microcontroller Interfacing. In: Book Design and Analysis of Integrated Circuit DC Parametric and Functional Testing Module with GUI using Matlab and Microcontroller Interfacing, 2021, pp. 1-10.

- 29. Pauzan M, Yanti I. Utilisation of ADC PIN on Arduino Nano to Measure Voltage of a Battery. *Teknokom*, 2021.

- Itterheimová P, Foret F, Kubáň P. High-resolution Arduino-based data acquisition devices for microscale separation systems. *Analytica chimica acta*, 2021, 1153:338294.

- Ko J, Berger R, Lee H, Yoon H, Cho J, Char K. Electronic effects of nano-confinement in functional organic and inorganic materials for optoelectronics. *Chemical Society Reviews*, 2021, 50(5):3585-3628.

- 32. Lin CL, Chang JH, Chen FH, Lai PC, Chen YC, Ke CH, Wu CE, Peng JT. New Driving Structure to Increase Pixel Charging Ratio for UHD

TFT-LCDs With High Frame Rate. *IEEE Access*, 2022, 10:85114-85126.

- 33. Chaturvedi CM, Singh VP, Singh P, Basu P, Singaravel M, Shukla RK, Dhawan A, Singh SP. 2.45GHz (CW) Microwave Irradiation Alters Circadian Organization, Spatial Memory, DNA Structure in the Brain Cells and Blood Cell Counts of Male Mice, Mus Musculus. In: Book 2.45GHz (CW) Microwave Irradiation Alters Circadian Organization, Spatial Memory, DNA Structure in the Brain Cells and Blood Cell Counts of Male Mice, Mus Musculus. 2011:10.

- 34. Hashim N, Mohsim A, Rafeeq R, Pyliavskyi V. New approach to the construction of multimedia test signals. *International Journal of Advanced Trends in Computer Science and Engineering*, 2019, 8(6):3423-3429.

- 35. Ghosh A, Shankar BU, Meher SK. A novel approach to neuro-fuzzy classification. *Neural Netw*, 2009, 22(1):100-109.

- 36. Lin T, Shi Y, Shu N, Cheng D, Hong X, Song J, Gwee BH. Deep learning-based image analysis framework for hardware assurance of digital integrated circuits. *Microelectronics Reliability*, 2021, 123:114196.

- 37. Song Y, Wu Q, Wang X, Wang C, Miao X. Two Memristors-Based XOR Logic Demonstrated With Encryption/Decryption. *IEEE Electron Device Letters*, 2021, 42(9):1398-1401.

- Jiao S, Feng J, Zhang L, Wu D, Shen Y. Optical Logic Gate Operations With Single-Pixel Imaging. *IEEE Journal of Selected Topics in Quantum Electronics*, 2023, 29(2):1-8.

- 39. Geasa M. Development of an Arduino-based universal testing apparatus. *Archives of Agriculture Sciences Journal*, 2022.

- Pallavi J, Mohan N. Improved BIST Design for Detecting Ageing Faults in Automotive ICs. In: Book Improved BIST Design for Detecting Ageing Faults in Automotive ICs, 2021, pp. 1701-1706.

- Oberoi A, Dodda A, Liu H, Terrones M, Das S. Secure Electronics Enabled by Atomically Thin and Photosensitive Two-Dimensional Memtransistors. ACS Nano, 2021, 15(12):19815-19827.

# DOI: 10.17725/j.rensit.2024.16.589

# Nanophotonic Devices for Radio Over Fiber Technologies in Telecommunications Networks

# Hanan Mahmood Shukur Ali

Al-Kitab University, https://www.uoalkitab.edu.iq/eng/ Kirkuk 36015, Iraq *E-mail: hanan.m.shukur@uoalkitab.edu.iq*

# Sirwan Kareem Jalal

Al-Qalam University College, https://alqalam.edu.iq/en/

Kirkuk 36001, Iraq E-mail: sirwan.jalal@alqalam.edu.iq

# Maher Waleed Saab

Al-Nukhba University College, https://alnukhba.edu.iq/ Baghdad 10013, Iraq

E-mail: maher.wa@alnukhba.edu.iq

# Sharmeen Izzat Hassan

Knowledge University, College of Engineering, https://knu.edu.iq/college/

Erbil 44001, Iraq

E-mail: sharmeen.hassan@knu.edu.iq

# Ghazwan Saleem Naamo Ghno

Al-Rafidain University College, https://en.ruc.edu.iq/ Filastin str., Baghdad 10064, Iraq

*E-mail: ghazwan.nemo@ruc.edu.iq*

# Saif Saad Ahmed

Al-Turath University College, https://alturathuniversity.com/ Baghdad 10013, Iraq

E-mail: saif.saad@turath.edu.iq

# Salama Idris Mustafa

Alnoor University College, https://alnoor.edu.iq/en/

Nineveh 41012, Iraq

# E-mail: salama.ideis@alnoor.edu.iq

Abdymanap Z. Pirmatov

Osh State University, https://oshmed.edu.kg/ Osh 723500, Kyrgyzstan

*E-mail: pirmatov@oshsu.kg*

Received February 08, 2024, peer-reviewed February 10, 2024, accepted February 12, 2024, published September 06, 2024.

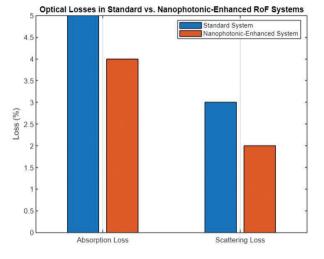

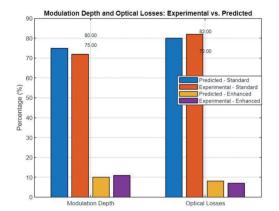

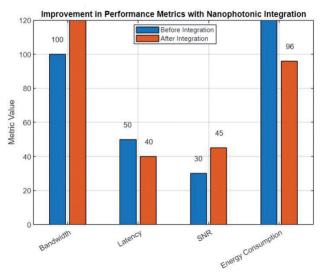

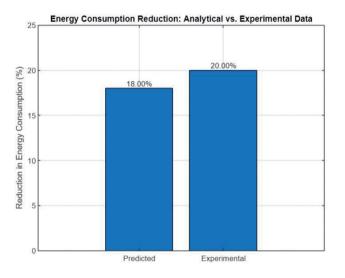

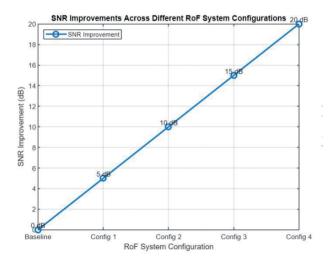

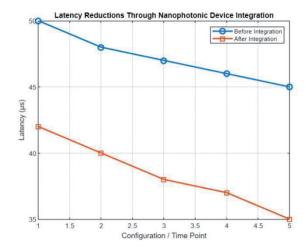

Abstract – <u>Background</u>: The combination of nanophotonic devices with Radio Over Fibre (RoF) technology has the potential to enhance telecommunications networks significantly. RoF technology, known for its ability to transport wireless data rapidly across optical fibres, has challenges such as capacity limitations and latency issues. Nanophotonic devices overcome these challenges using their small size and advanced ability to manipulate light. <u>Objective</u>: This study aims to investigate the capability of nanophotonic devices to improve the performance of RoF systems in telecommunications networks. It focuses on evaluating the system's energy efficiency, bandwidth, and latency caused by these devices. <u>Methodology</u>: The effectiveness of RoF systems combining various nanophotonic devices, including modulators, photonic crystals, and nanolasers, was assessed using experimental and computational methods. The research included quantifying and examining pivotal performance metrics, such as the mitigation of delay, the minimization of energy usage, and the augmentation of bandwidth. <u>Results</u>: Integrating nanophotonic devices into

#### 590 HANAN MAHMOOD SHUKUR ALI, SIRWAN KAREEM JALAL, MAHER WALEED SAAB, SHARMEEN IZZAT HASSAN, GHAZWAN SALEEM NAAMO GHNO, SAIF SAAD AHMED, SALAMA IDRIS MUSTAFA, A.Z. PIRMATOV

# RADIOELECTRONICS

RoF systems led to significant improvements, including a substantial increase in bandwidth, a decrease in latency, and an upgrade in energy efficiency. The progress above may be attributed to the nanophotonic devices' enhanced modulation and signal processing capability. *Conclusion:* Nanophotonic devices offer a practical alternative to the current limitations of RoF technology in telecommunications networks. Integrating these components into RoF systems can significantly enhance network performance, making it a promising path for developing telecommunications infrastructure in the future. Further investigation is recommended to explore the practicality of incorporating these devices into real-world networks and to ascertain their scalability.

*Keywords:* nanophotonic devices, Radio Over Fiber (RoF), telecommunications networks, bandwidth optimization, latency reduction, energy efficiency, photonic crystals, nano lasers, optical modulation, signal processing

## UDC 621.396.673, 621.396.96

*For citation:* Hanan Mahmood Shukur Ali, Sirwan Kareem Jalal, Maher Waleed Saab, Sharmeen Izzat Hassan, Ghazwan Saleem Naamo Ghno, Saif Saad Ahmed, Salama Idris Mustafa, Abdymanap Z. Pirmatov. Nanophotonic Devices for Radio Over Fiber Technologies in Telecommunications Networks. *RENSIT: Radioelectronics. Nanosystems. Information Nechnologies*, 2024, 16(5):589-604e. DOI: 10.17725/j.rensit.2024.16.589.

# **CONTENTS**

- 1. INTRODUCTION (590)

- 2. LITERATURE REVIEW (591)

- 3. NANOPHOTONIC DEVICES IN ROF TECHNOLOGIES (592)

- 4. METHODOLOGY (593)

- 5. RESULTS (598)

- 6. DISCUSSION (601)

- 7. CONCLUSION (602)

- REFERENCES (603)

# 1. INTRODUCTION

Radio Over Fibre (RoF) technology is a cuttingedge solution that combines radio frequency (RF) technology with optical fibre communications provide wide-ranging wireless broadband to connectivity. This integration facilitates the seamless transmission of radio frequency (RF) data across optical fibres, combining the extensive bandwidth capabilities of fibre optics with the global accessibility and flexibility of wireless communication [1,2]. The significance of RoF (Radio over Fibre) in the telecommunications sector is crucial as it efficiently addresses major obstacles like coverage restrictions, capacity constraints, and the growing demand for high-speed data services [3]. RoF technology plays a crucial role in advancing telecommunications infrastructure by enabling the efficient and highcapacity transportation of wireless signals, hence supporting the implementation of next-generation networks and services [4,5].

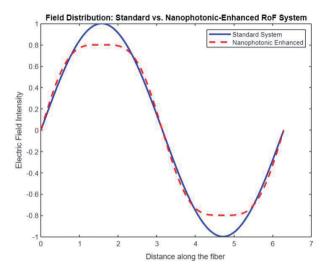

ability to alter light at the nanoscale, have the potential to revolutionise RoF systems. By harnessing the distinctive characteristics of the interaction between light and matter on a nanoscale scale, these devices, including photonic crystals, nanolasers, and optical modulators, achieve exceptional mastery over the creation, transmission, and detection of light [6,7,8]. The ability of nanophotonic devices to boost RoF technology lies in their capacity to improve system performance via smaller dimensions, lower energy consumption, and higher modulation speeds. A notable advancement in nanophotonic modulation methods is the development of a silicon optical single-sideband modulator with an unusually high sideband suppression ratio. This advancement offers a promising opportunity to improve the efficiency and functionality of RoF systems [9]. The current article examines how nanophotonic

Nanophotonic devices, characterised by their

devices may be integrated into RoF technologies, focusing on their ability to address existing limitations and enable the advancement of telecommunications networks. Our objective is to provide a comprehensive overview of how nanophotonic devices can enhance RoF infrastructures' functionality, effectiveness, and expandability. This will be achieved through a detailed analysis of the advancements in nanophotonic device technology, including their development, production, and integration into RoF systems. The study includes:

# NANOPHOTONIC DEVICES FOR RADIO OVER FIBER 591 TECHNOLOGIES IN TELECOMMUNICATIONS NETWORKS

- a thorough investigation of current RoF technologies,

- a detailed analysis of the latest nanophotonic devices and

- an evaluation of how they may impact the performance of RoF systems.

The article seeks to provide insights into the future of telecommunications by integrating theoretical research, simulation studies, and experimental validation. The confluence of nanophotonic devices with RoF technology showcases their ability to meet the growing demands for high-speed, high-capacity, and energy-efficient wireless communications [10,11,12,13].

## 1.1. The Study Objective

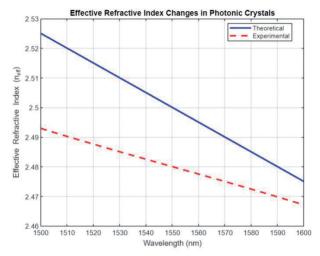

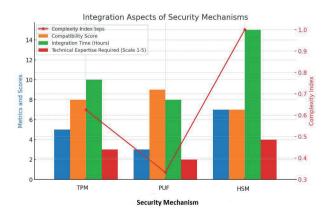

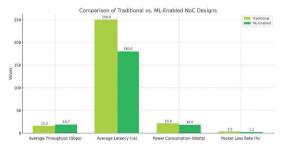

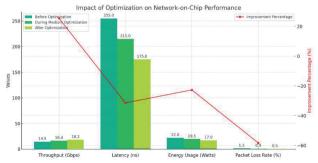

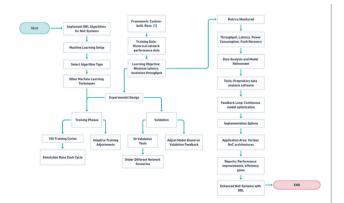

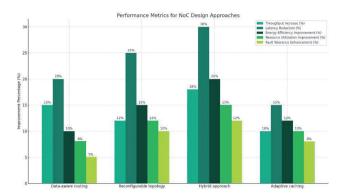

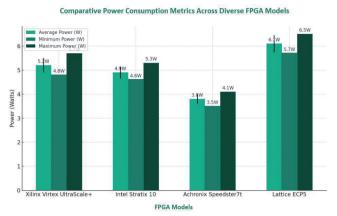

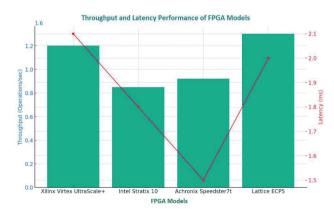

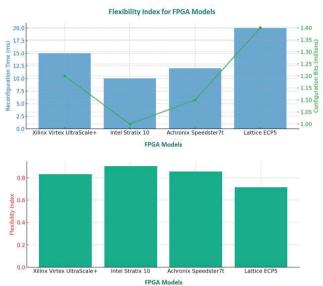

The article's primary objective is to comprehensively investigate the potential enhancements that may be achieved by integrating nanophotonic devices into Radio Over Fibre technologies to improve the performance of telecommunications networks. This study aims to demonstrate a correlation between the real-world applications of nanophotonic devices in RoF systems and their theoretical advantages, such as their small size, outstanding efficiency, and capacity to control light. The research focuses on assessing the capability of these devices to improve key performance indicators (KPIs) of RoF technology. The indicators consist of energy efficiency, bandwidth capacity, and signal delay.